【ベストコレクション】 短チャネル効果 リーク電流 152600-短チャネル効果 リーク電流

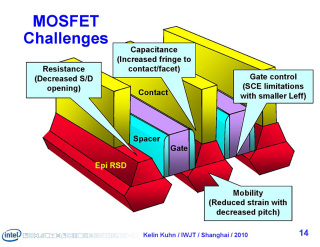

短チャネル 効果 消費電力or リーク電流 •Vdd • Vth design •EOT • Nsub •EOT •x j (ext conc) • Nsub • ゲート絶縁膜 トンネル電流 • 反転層容量 • ポリ空乏化 •Sファクター • 有限のSiバン ドベンディング • ソース抵抗 • 移動度 • 接合トンネル電流 • ゲート絶縁膜トンネル電流Cv の式からもわかるように、チャネルのな かの電荷が増えて、チャネル抵抗が下がり、 ドレイン電流が増加する。ここで断わって おくが、チャネル間は完全に抵抗と等価で はない。mosfet のソースドレイン間の電 圧電流特性からわかるように、飽和領域と短チャネル効果ー電流非飽和ー ピンチオフ電圧以上の飽和領域で電流が飽和しない vds i ds vds i ds 長チャネルmosfet ピンチオフ電圧で飽和 飽和電流は(v gv t)2に比例 ピンチオフ電圧で飽和しない 飽和電流は(v gv t)に比例 短チャネルmosfet v gの増大 v gの増大

プロセスインテグレーション デバイス 及び構造 Manualzz

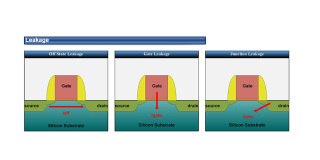

短チャネル効果 リーク電流

短チャネル効果 リーク電流-による駆動電流取得や短チャネル効果防_ll二に,浅い接合 は短チャネル効果防止にそれぞれ必要となる。特に,こ の世代のゲート絶縁膜は2nm程度と非常に薄くなること から,ゲート絶縁膜を貫通する直接トンネル電流による ゲート漏れ電流の問題が無視できなくなってくる。この 間題を回避する短チャネル効果 に 高移動度が要求されるTFTと低リーク電流 が要求されるTFTという2種類のTFTを最小限のプロセスの変更によって、量産性を維持しつつ、容易に作り分ける。 例文帳に追加 To easily manufacture two kinds of TETs, that is, a TFT for which high mobability is required, and a TFT for which low leakage currents are

第3回 Cmosデバイス 2 マイクロプロセサ Mosトランジスタと配線を学ぶ 日経クロステック Xtech

· 短チャネル効果とは何か 半導体デバイスは性能向上や1枚のウェハからとれるチップの数を増やしてコストを下げるため、ムーアの法則に従ってどんどん微細化が進んでいる。 ところが、デバイスの微細化に伴う副作用が発生する。 それが短チャネル効果と呼ばれる現象である。 短チャネル効果はいくつかあり、 ・ ドレイン誘起障壁低下 DrainInduced Barrier Loweringリーク電流の低減を可能とするマルチしきい値対応の 015μm fdsoi cmosデバイスを開発した。 mosデバイスではゲート長の縮小により駆動力は向上 するが,短チャネル効果が発生し,しきい値電圧が低下 する。これを抑制するため基板濃度を上げると,駆動力Gs間に1vの電圧を掛けても、まだチャネルはPのままなので、電流は流れない。 ② vgs=2v gs間に2V程度の電圧を掛けると、ようやくチャネルがNに反転して電流が流れ始める。⇒これがしきい値(vth) ③ vgs=45v on抵抗をしっかり下げるには、vthより十分に大きな電圧を与える。 vgs=45vで85mΩ、vgs=10v

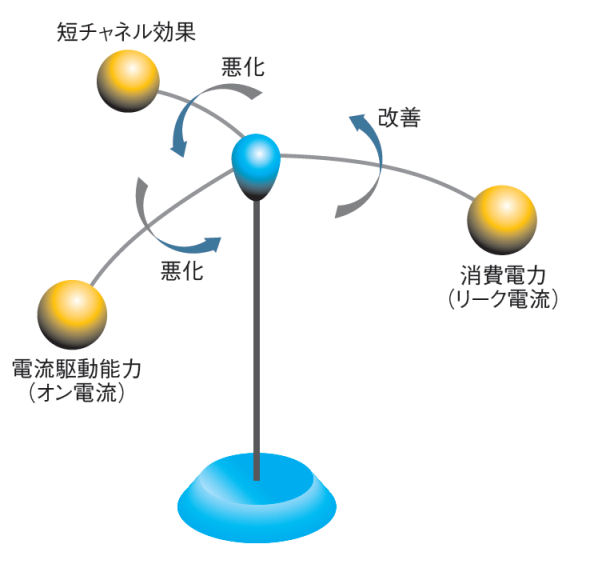

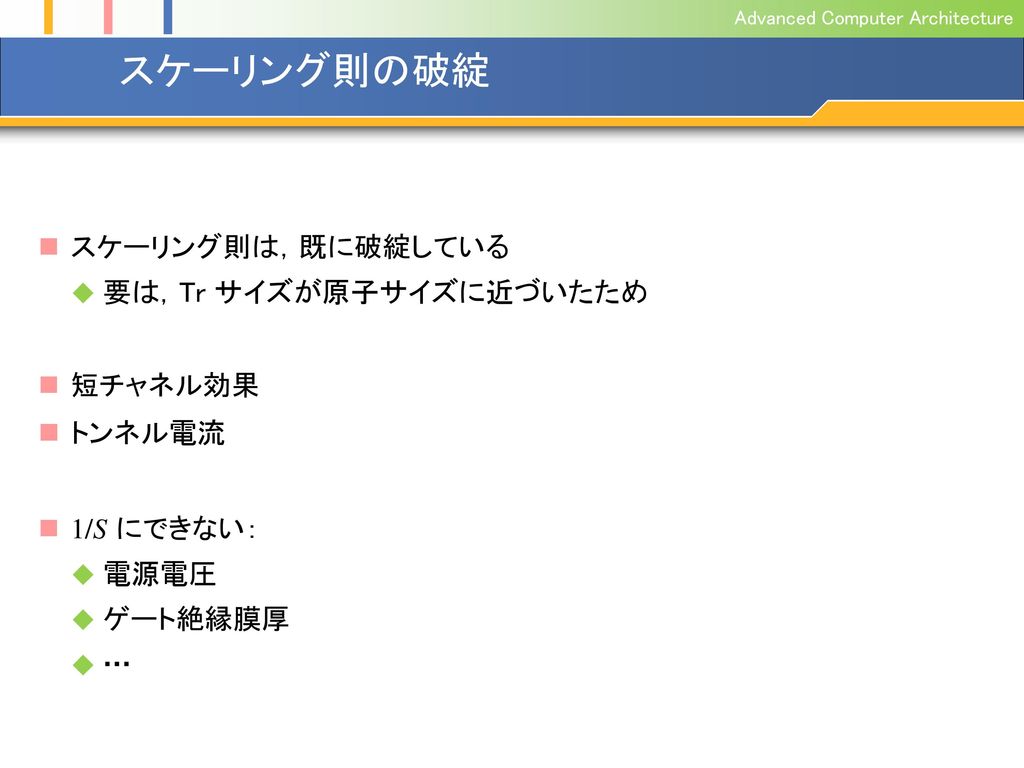

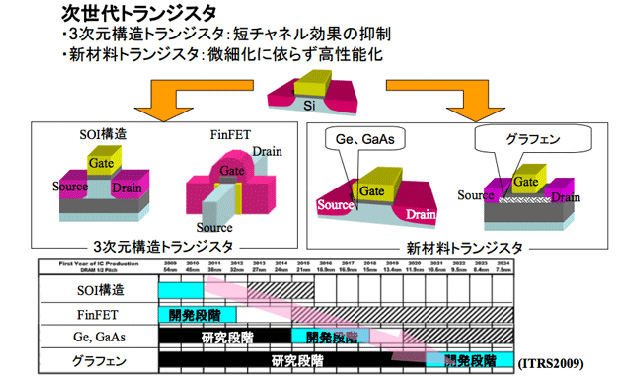

チャネル長50nmのDSSトランジスタの電流-電圧特性を 図8に示す。これまでと同様,良好なトランジスタ特性が得ら れている。50nm程度のチャネル長になると,寄生抵抗の低 減効果や,高い短チャネル効果耐性などのショットキートラン短チャネル効果の発生 → オフ電流の増大 → 消費電力増大 マルチゲート構造 の開発 対策 ゲート長の縮小 × ナノ領域では,電子の波動性がデバイス特性に顔を出す 量子閉じ込め効果,トンネル効果 ゲート絶縁膜の薄層化 反転層容量の影響が増大 → オン電流の減少 → 高速化に障害 "ON · 短チャネル効果を抑制 mosトランジスタは「微細化すると,駆動電流が増して高速動作し,消費電力が減少し,高密度化もできる」という好ましい特性を持っている。これに理論的裏付けを与えたのがスケーリング則 16) であり,恒常的な微細化を促進する力となった。 トランジスタの駆

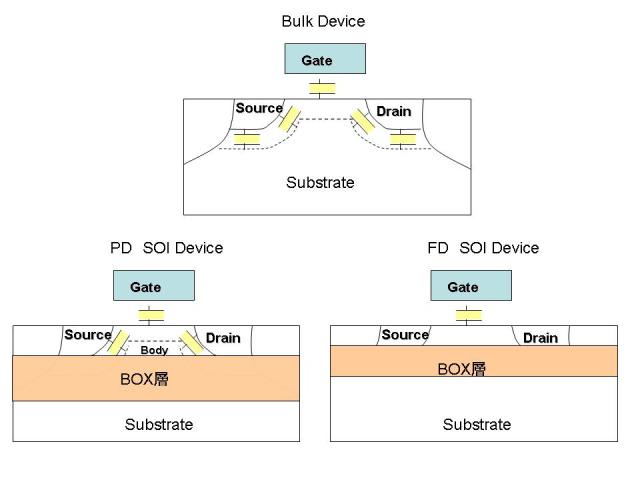

チャネル不純物量を増やすことができる。低しきい値化 と短チャネル効果抑制を両立できる。この斜めチャネル 注入プロセスで試作を行ったpmosfetのオン電流とオ フ電流の関係を図2に示す。短チャネル効果を十分に抑(3)図5 bの チャネルへの突き抜けによるフラットバン ド電圧変化 することが知られているチ ャネルのon/offを 決める閾 値電圧は正味のチャネル濃度に依存するので,閾 値電圧を制 御するためにはbの チャネル領域への拡散を抑制する必要 · このため、短チャネル効果を抑制できる。 さらに、Si基板の替わりとして完全空乏層SOI(Silicon on Insulator)基板を使う選択肢もある。 埋め込み絶縁層を導入したSOI基板を導入することで、ソース/ドレインと基板の接合容量を小さくでき、リーク電流を抑制できる。

学位論文要旨詳細

2

本節では,mosfet の短チャネル効果の諸現象とその代表的な対策方法について説明する. 311 短チャネル効果の諸現象 (1) しきい値電圧低下 狭義での短チャネル効果は,ゲート長を短くしていったときのmosfet のしきい値電圧 (v th)の低下を指す.vト容量が維持され、これによって短チャネル効果を抑制してリーク電流を削 減できます。図1 に、このチームが提案した2つの構造を示します。 dg(ダブルゲート)構造はゲート・リーク電流を最小化できる可能性があり ますが、これを回転するとゲート電極が自己整合しプレーナ型fetと同様のドレイン電流 I D (V GV T) 2に比例して増加する ドレイン電圧V D ドレイン電流 I D ゲート電圧に対してほぼ等間隔 傾斜 I v WC (V V) MOSFET μC (V V ) L W I MOSFET ds S ox gs TH ds o ox gs TH = − = − 2 1 2 短チャネル 長チャネル 実際はこの中間を取り、以下の表現を用いる場合

2

2

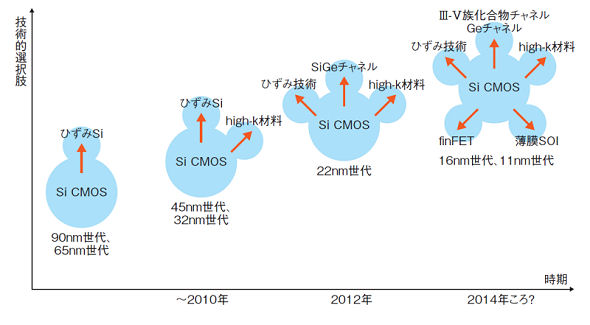

1) チャネル面積を大きくできることから、駆動電流量を大きくで きる。このため、より高速なデバイスを実現できる。 2) ゲート長が短くなると現れる短チャネル効果(オフ時、リーク電流が増える)、パンチスルー現象(ゲの低下やゲート絶縁膜薄膜化によるトンネルリーク電流増加に代表される短チャネル効果 等による寄生効果によって性能向上が妨げられることが明らかになった。その解決策として は、微細化によらない性能向上技術(歪み6lや歪み6l*h等の高移動 チャネル材料の採 用)、ゲートによる · マルチゲートにすることでゲートの支配力が増すのは分かります。 短チャネル効果とは、ゲートに電圧がかかっていない時 (すなわちオフ時)にも チャネルを電流が流れてしまう (オフ電流)という現象ですよね?

半導体の温故知新 6 Mosトランジスタの次はtfet 津田建二の技術解説コラム 歴史編 Edn Japan

Soiデバイス マイクロ ナノデバイス

So we had to improve RF performance remarkably We chose InAlN as a barrier of GaN HEMTs for high transconductance and developed low capacitance gate process, a key technology of RF performance improvement To reduce gate capacitance (Cgs), Yshaped gate process with short gate length of 100 nm was developed4 短チャネル効果低減 微細化 5 バックゲート効果低減 安定動作、アナログ対応 6 サブスレッシュ・ホールド・スロープ低減 低電圧動作対応 7 リーク電流減少 高温動作対応 8 耐ノイズ性の向上 アナログ・デジタル混載容易 9 耐放射線性の向上 耐環境応用子トンネル効果によって酸化膜を透過して流れ出るゲートリーク電流が恒常的に 発生し、トランジスタとして正常に機能しなくなって来ている。ゲートリーク電流 に対する先行的取り組みとしては、highk ゲート酸化膜2と呼ばれる、ゲート絶

2

2

チャネル長変調効果 ピンチオフ点よりもドレイン側では完全に空乏化している。 この空乏層はドレイン電圧が高くなると伸びて、 ピンチオフ点をソース側に押しやる。 したがって、実効的なチャネル長が短くなり、電流を増加させる。 これをチャネル長変調というに高濃度不純物が不要(SOI層の薄膜化により,短チャネル 効果を抑制)のためキャリアの高移動度が実現でき(基板不 純物とのクーロン散乱の抑制),また,厚い埋込み酸化膜構 造によるソース/ドレイン接合の低容量化が達成できるた め,非常に有望な素子構造である。 しかし,通常のSi短チャネル効果とは、 一般にチャネル長を微細にしたり、ドレイン電圧を印 加することで、ゲート電圧のチャネル電流に対する制 御力が低下し、閾値電圧が低下する現象である。素子 作製上、リソグラフィーによって形成しているmosfetのチャネル長が、素子間である程度ばらつくこと

Vlsi 10 東芝 16nm以降で役立つナノワイヤトランジスタを高性能化 プロセス技術 Ee Times Japan

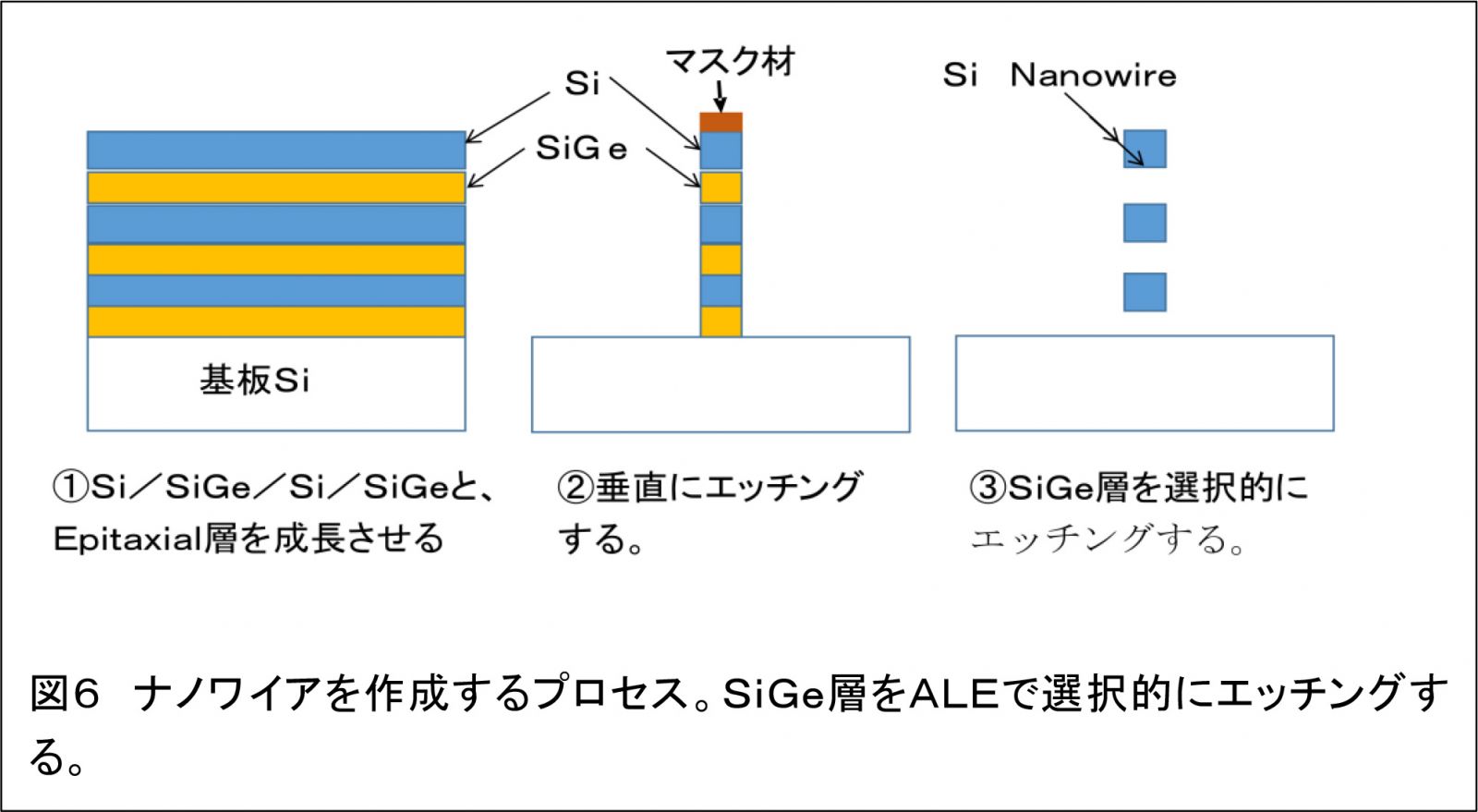

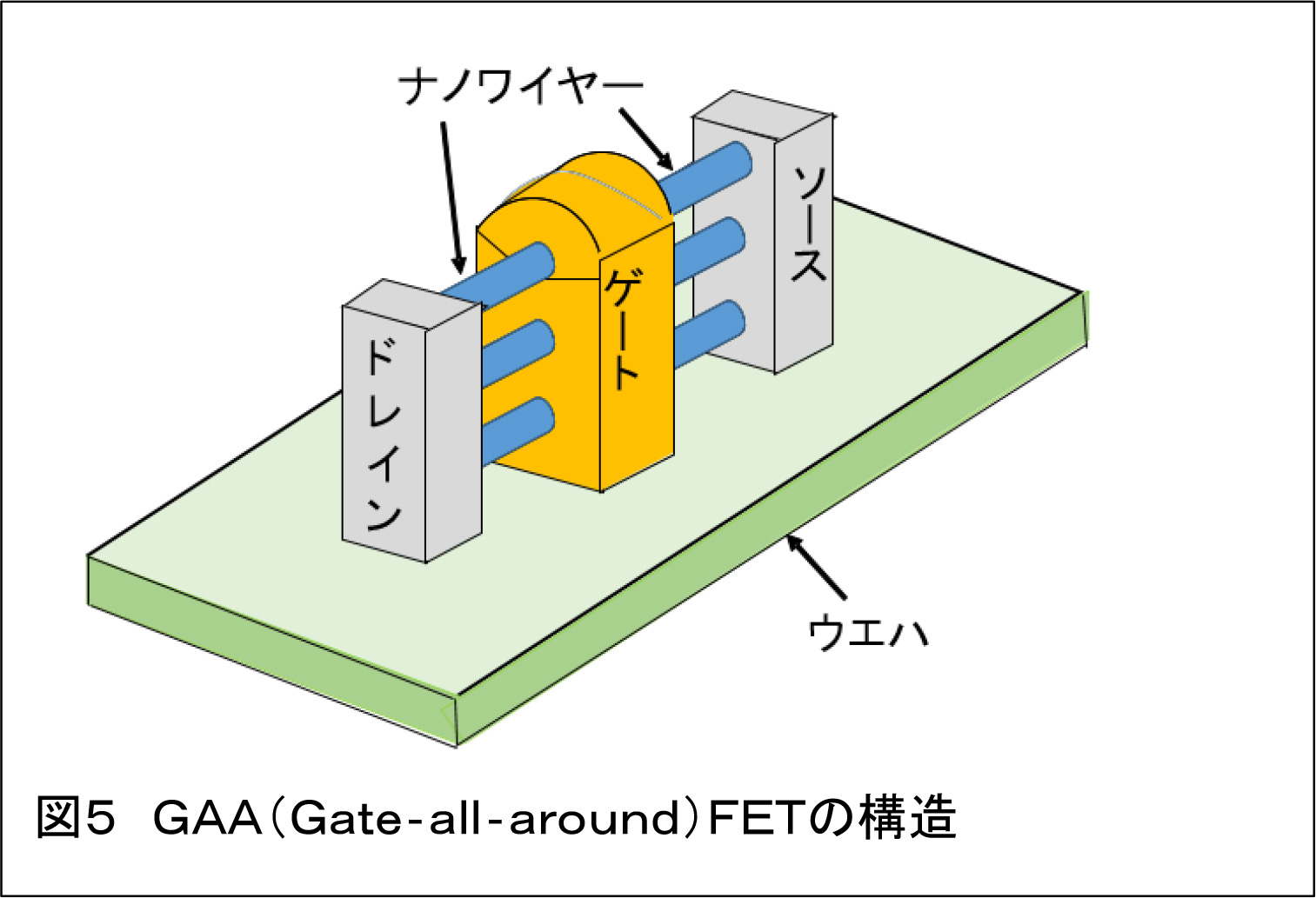

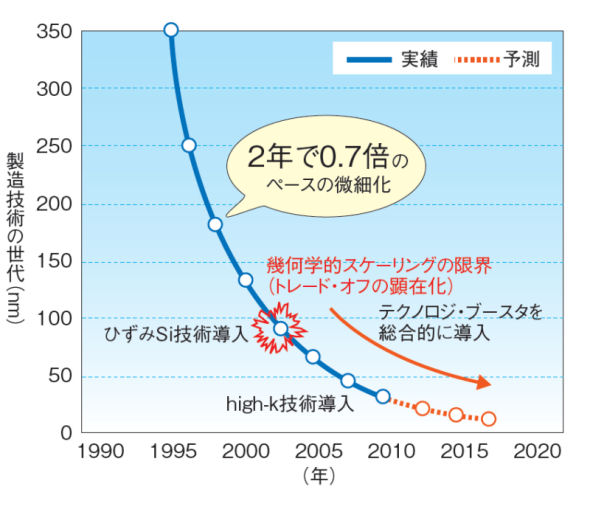

微細化の限界に挑む Siと新材料の融合で新たな展望も プロセス技術 3 10 ページ Ee Times Japan

Wdmを小さくすると短チャネル効果が抑えられるがBody効果が増加して回路性能が落ちる。toxを薄くすればゲート支配力が増加し電流が増えるが信頼性は低下する。 短チャネル抑制のためには Lmin/(m×Wdm)≒2にするのが良い。Lは設計上のLよりは小さくなる。 サブスレショルドプローブ23mkT/qとBody• チャネル長変調 • 短チャネルデバイス – 短チャネル効果(電荷配分) – ドレイン~ソース電圧の効果 – 逆短チャネル効果 • 狭チャネルデバイス – 狭チャネル効果 – 逆狭チャネル効果 • パンチスルー • キャリア速度飽和 • ホットキャリア効果 · る短チャネル効果,基板不純物の表面蓄積(パイルアップ現象)や短チャネ ル効果を防止する目的のドレイン・ソース端の高濃度不純物注入(ポケット 注入)により,逆にスレショルド電圧が増大する逆短チャネル効果,ゲート酸 化膜厚の薄膜化と基板の高濃度化によるチャネル表面の量子化

2

Ascii Jp 半導体プロセスまるわかり カーボンナノチューブと450mmウェハー 2 3

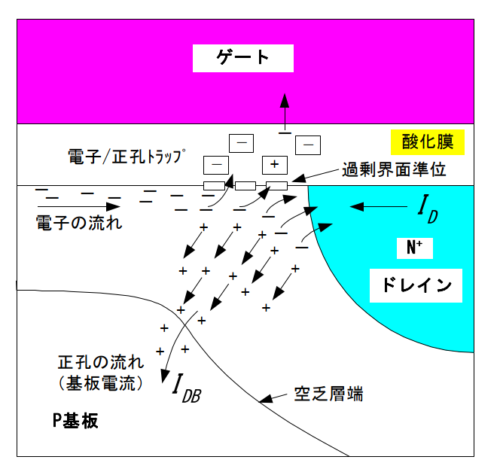

短チャネル効果 英語表記:Short Channel Effect 微細化によるMOSトランジスタのチャネル長が短くなると、ゲート電圧でチャネルを閉じても、チャネル下部を流れるリーク電流が増えてくる。これは、ドレインの電界がソースに届くようになり、ソース端の障壁の問題が見えてきており,mosfetの短チャネル効果 抑制と高い電流駆動力の両立が大変困難になってきてい る.したがって従来型の平面形mosfetの高性能化と 同時に,新規構造デバイスへの研究開発の注力度がここ 数年高まっている. finfetは従来型と異なる三次元構造のmosfetで あり,久本らがドレイン電流がドレイン電圧に対して飽和する mosトランジスタの電圧電流特性 ドレイン電圧が上がると,ドレインからの電界の影響でドレイン近傍に電子が 存在できなり、チャネル右端がドレイン左端に等しくなる時をピンチオフという (チャネル)

テクニカルレポート Busicom Post

2

② 短チャネル効果に伴うソース・ドレイン間のリーク電流,ゲート絶縁膜を通したゲート リーク電流が顕在化し,無効電力が急激に増加する ③ 微細加工プロセスにおける精度,活性領域における不純物の分布などに起因する素子性間とに流れる漏れ電流(Gate Leak Current ゲートリーク電流)の増大による消費電 力の増大、多結晶シリコン(polySi ポリシリコン)のゲート電極がゲート絶縁膜との界 面近傍で空乏化することによるドレイン電流駆動能力の低下が大きな課題として浮 上してきた。更なるMOSFETの性能向上には、ゲートリーク電流の低減、ゲート電極

短チャンネル効果のないigzo利用のmosトランジスタ セミコンポータル

テクニカルレポート Busicom Post

2

00 号 半導体装置及びその製造方法 Astamuse

2

リーク電流 Wikipedia

第3回 Cmosデバイス 2 マイクロプロセサ Mosトランジスタと配線を学ぶ 日経クロステック Xtech

2

2

2

学位論文要旨詳細

2

ニュースリリース 10 12 06 立体構造トランジスタの高性能化技術の開発について ニュース トピックス 東芝

Leap Lsi消費電力削減のためmosの Vt低減 不揮発性メモリに力点 セミコンポータル

2

00 号 半導体装置及びその製造方法 Astamuse

東京工業大学 最近の研究成果 研究成果詳細

2

Iedm 10 東芝 立体構造トランジスタの高性能化技術を開発 Tech

学位論文要旨詳細

第3回 Cmosデバイス 2 マイクロプロセサ Mosトランジスタと配線を学ぶ 日経クロステック Xtech

微細化の限界に挑む Siと新材料の融合で新たな展望も プロセス技術 3 10 ページ Ee Times Japan

シャロートレンチアイソレーション Wikiwand

2

2

2

微細化の限界に挑む Siと新材料の融合で新たな展望も プロセス技術 3 10 ページ Ee Times Japan

11 省電力 五島 正裕 Ppt Download

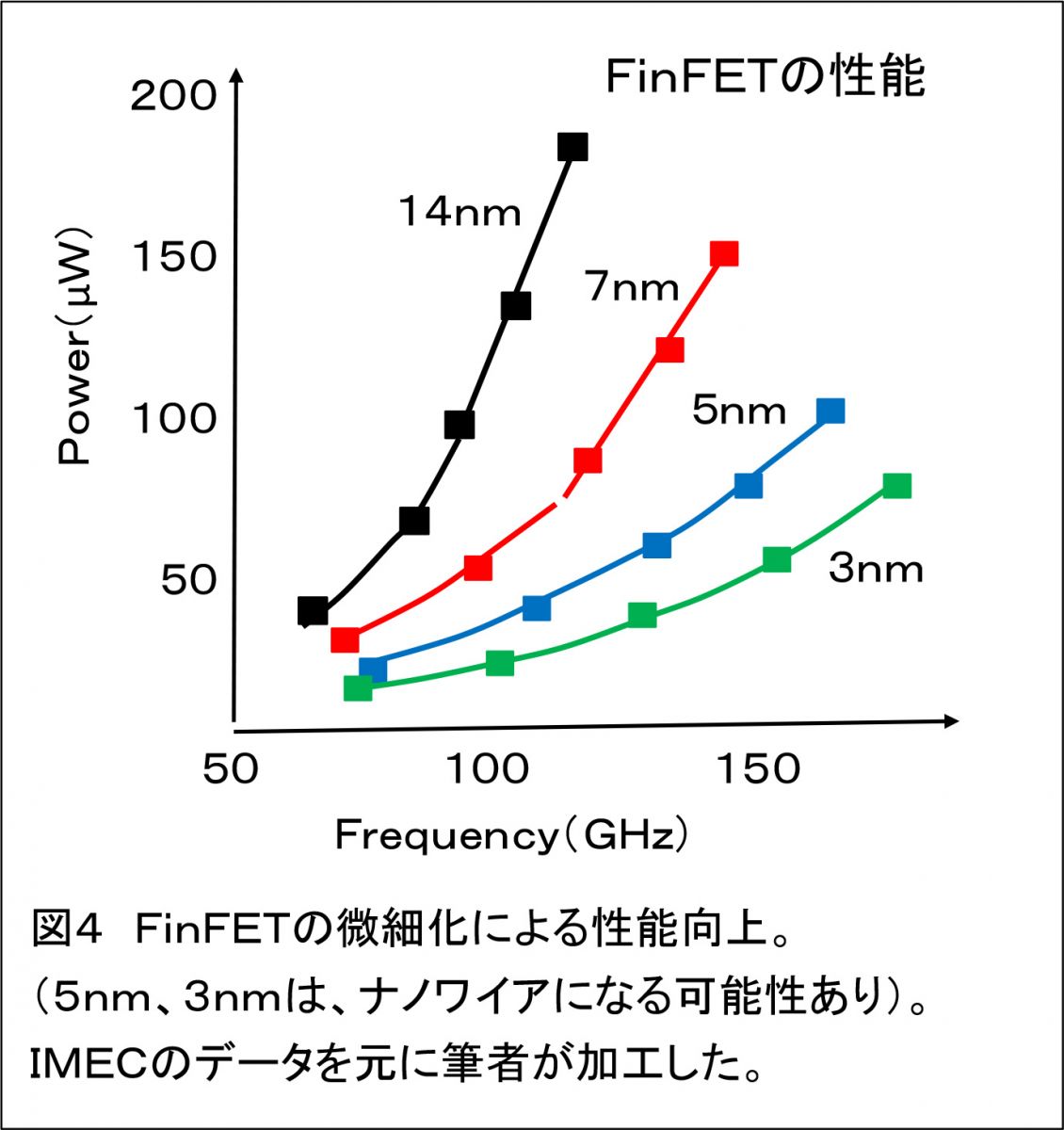

半導体業界の話題 第9回 エレクトロニクス業界の発展を牽引してきた ムーアの法則 はさらに続く ピックアップ プリント基板の窓口 プリント基板設計 製造 実装の最適な発注先が見つかる

後藤弘茂のweekly海外ニュース Intelの Broadwell を支える強力な14nmプロセス Pc Watch

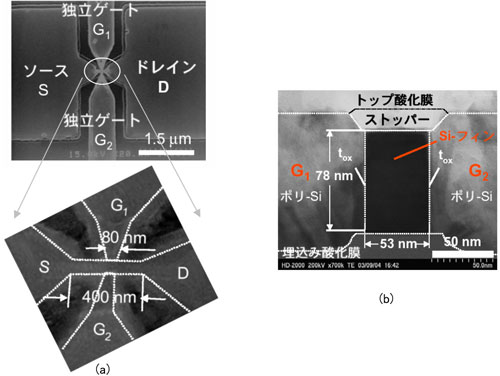

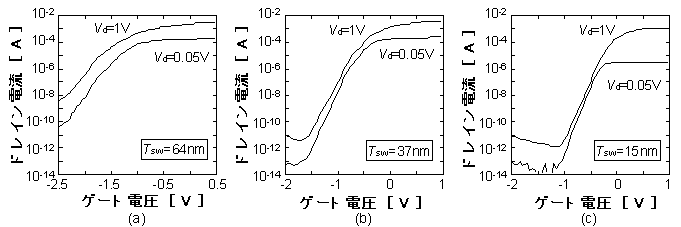

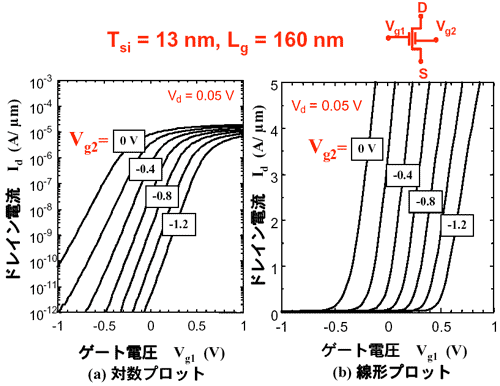

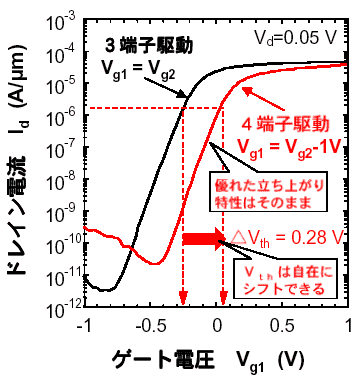

産総研 4端子駆動型ダブルゲートmosfetの開発に成功

2

Cmosデバイス設計 マイクロ ナノデバイス

半導体装置及びその製造方法

2

電子機器開発者のための半導体パッケージ熱設計入門 待ったなし Soc Sipの熱対策 Tech Village テックビレッジ Cq出版株式会社

2

学位論文要旨詳細

2

2

2

産総研 新開発プロセスによる世界最薄縦型ダブルゲートmosfetの作製に成功

寒川誠二教授の研究グループ 超低損傷中性粒子ビーム酸化プロセス技術による12ナノメートル世代以降の高品質ge Mosトランジスタ構造を実現 Aimr

Finfetのアナログ適用 デジタル回路が不可欠 日経クロステック Xtech

Finfetのアナログ適用 デジタル回路が不可欠 日経クロステック Xtech

2

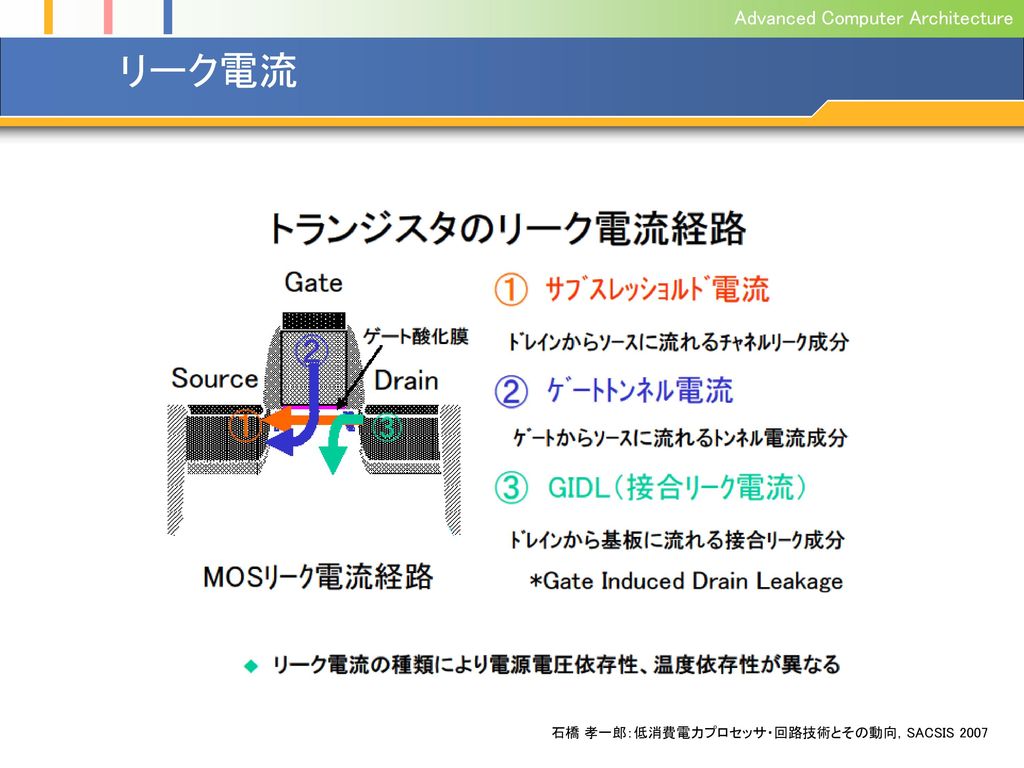

再録 コンピュータアーキテクチャの話 5 リーク電流の影響 Tech

04 号 短チャネル効果を抑制したmis型電解効果トランジスタ Astamuse

ニュースリリース 10 12 06 立体構造トランジスタの高性能化技術の開発について ニュース トピックス 東芝

2

短チャネル効果とは何か 半導体物理 Sciencompass

2

2

Mosfetスケーリング マイクロ ナノデバイス

2

テクニカルレポート Busicom Post

Leap Lsi消費電力削減のためmosの Vt低減 不揮発性メモリに力点 セミコンポータル

学位論文要旨詳細

2

2

産総研 4端子駆動型ダブルゲートmosfetの開発に成功

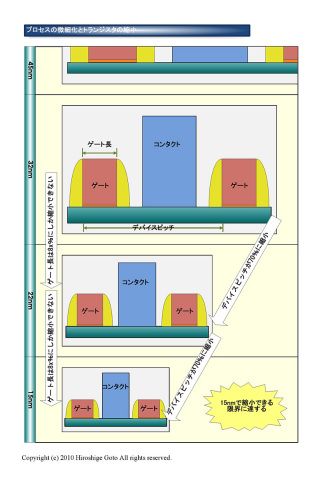

プロセスインテグレーション デバイス 及び構造 Manualzz

2

2

後藤弘茂のweekly海外ニュース Intelの Broadwell を支える強力な14nmプロセス Pc Watch

11 省電力 五島 正裕 Ppt Download

東北大 高性能 サブ10nm 3次元フィン型ゲルマニウムトランジスタ作製に成功 Fabcross For エンジニア

2

2

2

2

00 号 半導体装置及びその製造方法 Astamuse

後藤弘茂のweekly海外ニュース Intelの Broadwell を支える強力な14nmプロセス Pc Watch

2

半導体業界の話題 第9回 エレクトロニクス業界の発展を牽引してきた ムーアの法則 はさらに続く ピックアップ プリント基板の窓口 プリント基板設計 製造 実装の最適な発注先が見つかる

2

東京工業大学 最近の研究成果 研究成果詳細

2

限界を超えた薄型トランジスター Nature ダイジェスト Nature Portfolio

00年代 新構造デバイスの模索 集積回路 今日までlsi業界の発展を支えてきた基本原理の一つは 1974年にibmのr Dennardらが提唱したmosfetのスケーリング則 1 である 即ち バルクsiの上に作製した平面型mosfetの寸法を物理的に一定の比で

04 号 短チャネル効果を抑制したmis型電解効果トランジスタ Astamuse

2

04 号 短チャネル効果を抑制したmis型電解効果トランジスタ Astamuse

2

産総研 4端子駆動型ダブルゲートmosfetの開発に成功

2

コメント

コメントを投稿